Aperçu une erreur? Envoyez-nous votre commentaire! Spotted an error? Send us your comment! https://forms.gle/hYPC8Auh6a4q52qT7

# **Examples of processes**

- Etching processes of Si-based materials

- SiO<sub>2</sub>

- Si<sub>3</sub>N<sub>4</sub>

- Si

Micro and Nanofabrication (MEMS)

In this lesson we will give examples of a few dry etching processes of silicon based materials. We will subsequently discuss dry etching of silicon dioxide, silicon nitrite, and silicon itself.

## Silica (SiO<sub>2</sub>) etching

- Removal of Si and O atoms needed

- SiF<sub>4</sub>, SiF<sub>2</sub>

CO<sub>x</sub>, COF<sub>2</sub>

Use of C, F chemistry (C<sub>2</sub>F<sub>6</sub>, CHF<sub>3</sub>, CF<sub>4</sub>), resulting in volatile SiF<sub>4</sub>,CO, and CO<sub>2</sub>

- AND energetic ions to break Si-O bonds (low pressure, hence energy >100 eV)

- F/C ratio chosen between the etch and deposition regime

- Wall reactor heating (>150 °C) to avoid polymer deposition

Micro and Nanofabrication (MEMS)

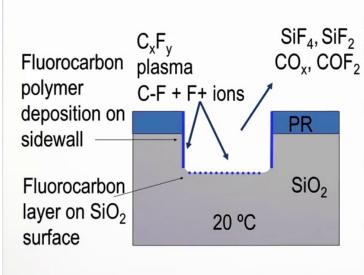

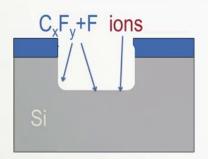

Etching of silicon dioxide, or silica, requires breaking silicon-oxygen bonds and the removal of both silicon and oxygen atoms. In practice, one uses frequently carbon and fluorine chemistry generating volatile reaction compounds like silicon tetrafluoride, carbon monoxide, and carbon dioxide. Due to the stable silicon-oxygen bonds, one needs energetic ions to break these bonds. So one etches at low pressure where it is possible to have such highly energetic ions. The fluorine to carbon ratio is chosen in the middle between the etch and deposition regimes so that etching in the vertical direction occurs, while in the horizontal direction, where there is no electrical field, there is polymerization and hence no mask underetching. The substrate is kept at room temperature during etching but the wall of the reactor can be heated at higher temperature to avoid polymer deposition there.

# Mask materials for silica etching

Micro and Nanofabrication (MEMS)

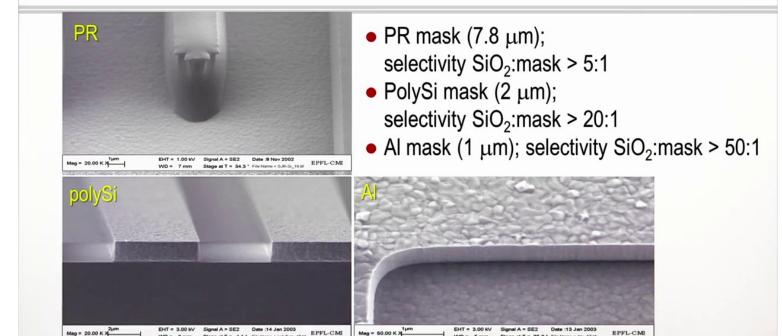

This slide shows a few pictures of mask materials that are used for silica etching. The first pictures presents a photoresist mask and one obtains here a selectivity towards silica etching of 5:1 for the conditions of the plasma used. That means the silica etches five times more rapidly than the photoresist. Polysilicon is a better masking material and one obtains a selectivity of 20:1. An aluminium mask is even better and has a selectivity of 50:1.

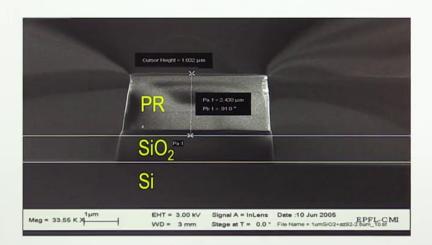

## Silica etching with photoresist mask

- SiO<sub>2</sub> thickness 1 μm

- Selectivity PR:SiO<sub>2</sub> = 1:5

- Gas: C<sub>4</sub>F<sub>8</sub> with CH<sub>4</sub>

- Pressure: 5 × 10<sup>-3</sup> mbar

- Etch rate: 0.25 μm/min

Micro and Nanofabrication (MEMS)

This picture shows the result of the silica etching using a photoresist mask. The silicon dioxide layer that was etched has been deposited on a silicon wafer. One sees that the photoresist is more attacked on the top corners and is slowly eroded by the etching process. As gas for this etching, one has used C4F8 with CH4 at a pressure of  $5x10^-3$  millibar. The silica etch rate was 0.25 micrometer per minute.

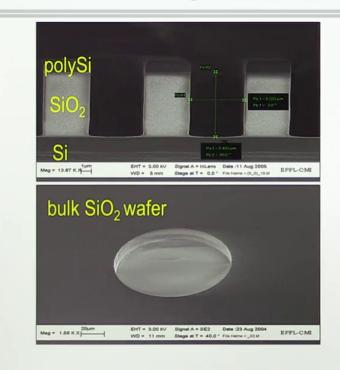

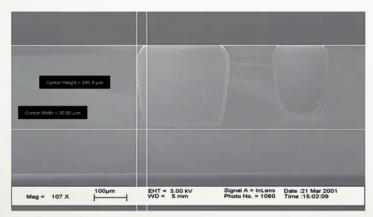

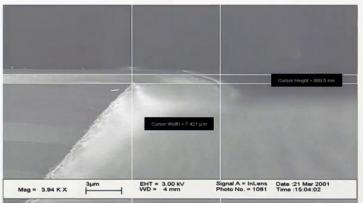

## Silica etching with polySi mask

- SiO<sub>2</sub> thickness 9 μm

- Mask material: polySi

- Selectivity polySi:SiO<sub>2</sub> = 1:20

- Gas: C<sub>4</sub>F<sub>8</sub> with CH<sub>4</sub>

- Pressure: 5 × 10<sup>-3</sup> mbar

- Etch rate: 0.45 μm/min

Micro and Nanofabrication (MEMS)

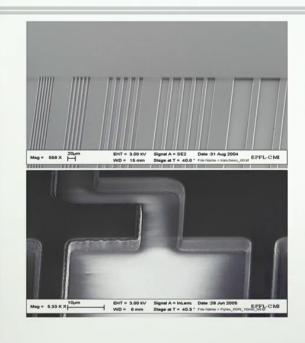

The top picture illustrates the etching of silica using a polysilicon mask. The silica layer that was deposited on the silicon substrate had the thickness of 9 micron. One uses the same gases as in the previous slide but one can vary, of course, composition and substrate bias to optimize the anisotropic etching. The lower picture shows a circular hole that has been etched in a bulk silica wafer using a polysilicon mask.

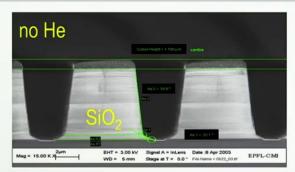

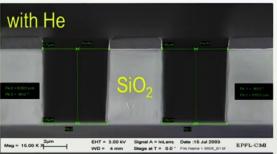

#### Silica etching by adding He gas flow

- Gas: high C/F ratio using C<sub>4</sub>F<sub>8</sub>

with CH<sub>4</sub> or H<sub>2</sub>

- Pressure: 5 × 10<sup>-3</sup> mbar

- He flow improves vertical etching (increases residence time of active species in a hole)

- High substrate voltage biasing (typically 300 V)

Micro and Nanofabrication (MEMS)

This slide illustrates a particular process that uses helium gas in combination with a halocarbon plasma with high carbon to fluorine ratio. That means one uses C4F8 with CH4 or hydrogen. The top picture is the result of the etching without helium gas. And one sees that the sidewalls are not vertical. This changes when we add helium gas and one can obtain much more vertical sidewalls. The helium gas is inert but it is believed to increase the residence time of the active species at the bottom of the etched structures because of collisions with the helium gas. That is why etching becomes more efficient there resulting in more vertical sidewalls of the etched structures. In this example, one has used a strong negative substrate voltage bias of minus 300 volts.

#### **Pyrex etching**

- Borosilicate glass or Pyrex has a typical composition 80 SiO<sub>2</sub> + ~10 B<sub>2</sub>O<sub>3</sub> + 2 Al<sub>2</sub>O<sub>3</sub> + ~5 Na<sub>2</sub>O

- Properties of Pyrex: low thermal expansion coefficient 3-5 ppm/°C, high chemical durability

- Etching mask material: Si

- Selectivity Si:Pyrex = 1:10

- Etching gas: C<sub>4</sub>F<sub>8</sub> with CH<sub>4</sub>

- Pressure: 5 × 10<sup>-3</sup> mbar

- Etch rate: 0.45 μm/min

Micro and Nanofabrication (MEMS)

Pyrex, or borosilicate glass, has as ingredients mainly silica, but it contains also boron oxide, aluminium oxide, and sodium oxide. Pyrex is an interesting material because it has a low thermal expansion coefficient and a high chemical durability. In dry etching, one can use silicon as mask material and one obtains a selectivity towards Pyrex of 1:10 for a typical halocarbon gas etching condition. The pictures show dry etched channels and a chamber made in a Pyrex wafer.

## Si<sub>3</sub>N<sub>4</sub> etching

- Si<sub>3</sub>N<sub>4</sub> main application is in membrane fabrication, as barrier layer in high-temperature oxidation processes, and as mask material for Si wet etching

- Both Si and N atoms need to be removed

- Pure F chemistry (SF<sub>6</sub>) or F, C chemistry (C<sub>2</sub>F<sub>6</sub>, CHF<sub>3</sub>, CF<sub>4</sub>) can be used

- F atoms form SiF<sub>4</sub> and eventually C atoms form CN, but etching works without presence of C

- Energetic ions needed to break Si-N bonds

Micro and Nanofabrication (MEMS)

Silicon nitrite is an interesting material in microfabrication and is often used for thin membrane fabrication, as barrier layer in high-temperature oxidation processes, and as mask material for silicon wet etching. The siliconnitrogen bond is a stable one and needs to be broken for etching to occur and subsequently the nitrogen and silicon atoms need to be removed. Pure fluorine chemistry with the gas SF6 or halocarbon chemistry gases can be used. The reaction product is silicon tetrafluoride. Also, in this case, energetic ions are essential to break the silicon-nitrogen bonds so negative substrate bias is important.

## Si etching

- Room-temperature deep anisotropic continuous etching process

- Room-temperature deep anisotropic pulsed process or Bosch process

- Cryogenic process

Micro and Nanofabrication (MEMS)

Now we will discuss three silicon etching processes. First, there is the deep anisotropic continuous etching of silicon at room temperature; then there is the anisotropic pulsed process, also known as the Bosch process, at room temperature; finally, we present a cryogenic process for silicon etching.

## Deep dry etching of Si: continuous process

- Example: combining SF<sub>6</sub> and C<sub>4</sub>F<sub>8</sub> chemistries,

whereby C<sub>4</sub>F<sub>8</sub> is the passivation gas

- Etching and passivation are simultaneous

- Substrate temperature typically is 20 °C

- Low etch rate: 1 to 3 μm/min (good control possible)

- High selectivity to photoresist : > 50

- Smooth sidewalls, very anisotropic process

Micro and Nanofabrication (MEMS)

We have already seen this slide before and it illustrates the continuous dry etching process for silicon. We already explained before how one can combine the etching gas SF6 and the polymerization gas C4F8 to obtain anisotropic silicon structures using photoresist as a mask.

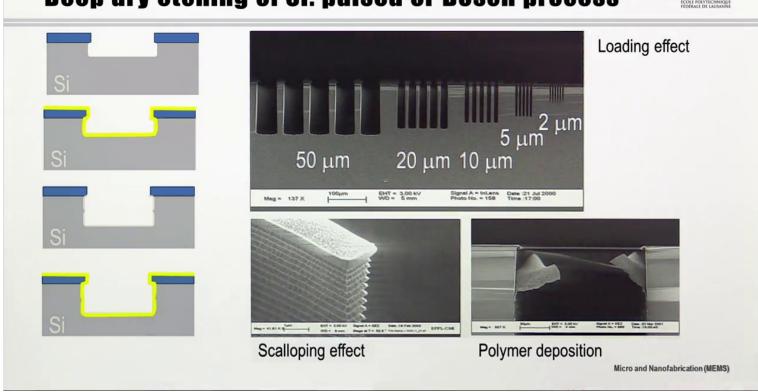

## Deep dry etching of Si: pulsed or Bosch process

We also have already introduced the dry etching of silicon using the pulsed, or Bosch, process. Here one alternates in time the etching and the polymerization cycles. The picture on top shows how wider holes get etched deeper than the narrower holes because the gas can enter more easily a wider hole. The fact that the depth of the etching is not the same everywhere is also called the <i>loading effect</i>. The picture at the lower left shows a detail of the structure with a scalloping effect characteristic for the Bosch process. One can clearly discriminate the different cycles of etching and passivation. The picture on the lower right shows a whole structure with still polymer layers that were attached to the side walls.

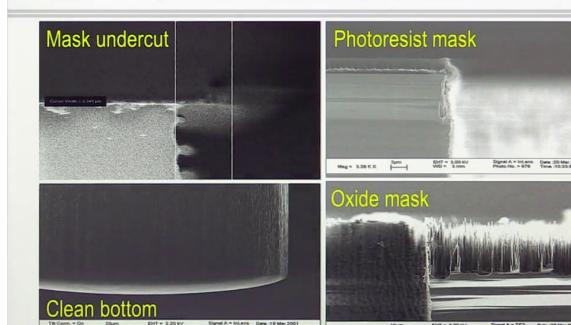

#### Surface quality of pulsed process

Mask material redeposition and formation of 'grass'

Micro and Nanofabrication (MEMS)

The surface quality of etched microstructures in the pulsed process depends on the used etching conditions. We already have seen that the scalloping effect gives rise to non-planar sidewalls. If this corrugation is too important, one can reduce the etching and polymerization cycle duration. Sometimes when polymerization is not sufficient, we can see mask underetching, so here was the mask and there is a lot of attack in this direction, so there was strong mask underetching. By increasing the relative importance of polymerization one can avoid such mask undercut like shown in this picture, which has the correct vertical wall at the right position. The picture here shows the bottom of an etched structure with a very smooth character. This was under good etching conditions. Sometimes one has redeposition of mask material into the hole which results in local micromasks that resist to the etching resulting in the formation of so-called "grass", as we see in this picture.

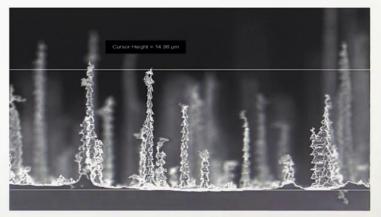

#### Surface quality of pulsed process

Bad equilibrium between etching and polymerization

- too much polymerization: grass formation

- not enough polymerization: disappearance of structure

Micro and Nanofabrication (MEMS)

The balance between etching and polymerization in the pulsed process is very delicate. If there is too much polymerization, micromasking effects due to the presence of polymer on the horizontal parts of the structure can give grass formation. When there is not enough polymerization the structure can simply disappear completely and one etches away all silicon. Here we see what was left from a silicon microstructure that has disappeared almost completely due to important etching in the horizontal direction, due to a lack of polymerization.

## **Shape control of pulsed process**

Higher pressure (0.1 mbar): bad control of the shape at the lower part of the microstructure

Lack of passivation: formation of local lateral holes on sidewalls

Micro and Nanofabrication (MEMS)

Also the pressure of the etching gas is important. When it is too high, the mean free path in the gas is low which can give rise to reduced gas access and removal of reaction products from the bottom of a hole structure. Therefore at the bottom of an etched structure we can have less vertical sidewalls as shown in this picture. This picture shows a condition where there was not enough polymerization. So in this case, not everywhere one has coated with polymer, and then laterally etched holes in the silicon appear.

## **Shape control of pulsed process**

Non-equilibrium between etching and polymerization: not enough passivation leads to bad shape

Micro and Nanofabrication (MEMS)

These two pictures illustrate other consequences of having not enough polymerization. This picture shows some bowing effect, some mask underetching, while the right picture shows a much higher width at the top than at the bottom, which is clearly a consequence of insufficient polymerization.

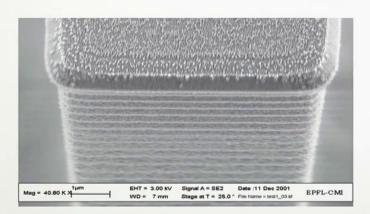

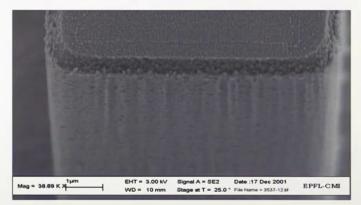

## Reducing the scalloping in the pulsed process

Gas application times  $SF_6 / C_4F_8 = 7 s / 2 s$

Gas application times  $SF_6 / C_4F_8 = 3 s / 1 s$

Micro and Nanofabrication (MEMS)

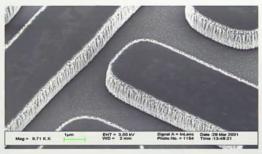

The scalloping effect of the pulsed process is again shown on this slide. The picture on the left shows a corrugation that is obtained when applying gas application times of 7 seconds for the etching gas and 2 seconds for the polymerization gas. If this roughness is too important one can reduce these times. The structure on the right was obtained by gas application times of 3 seconds and 1 second respectively. And indeed, this structure benefits from a much reduced corrugation, hardly recognizable on this picture.

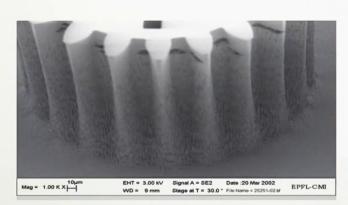

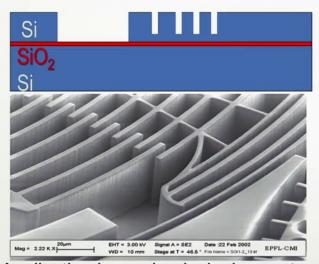

# Deep dry etching of Silicon on Insulator (SOI) wafers using the pulsed process

Application in mechanical microsystems and inertial sensors with electrostatic actuators

Micro and Nanofabrication (MEMS)

For some micromechanical applications, it is necessary to realize locally freestanding structures with vertical sidewalls. By applying a voltage between a freestanding structure and a fixed structure, one can, via electrostatic forces, activate the movable part- for example, if this is a fixed electrode, and if one applies a voltage here, it will attract the movable part in a certain direction. An elegant way to realize such micromechanical devices is by using silicon on insulator wafers. These special wafers have a silicon dioxide layer embedded and beneath this layer is single crystalline silicon, on top of this layer is also single crystalline silicon. If one etches through the top silicon to reach the oxide one can then simply remove the silicon dioxide so that the top layer becomes suspended. So in this way we can make freestanding parts. These pictures show finger-like electrodes made by the pulsed etching process. And here one has etched through 50 micrometer, that is this dimension, or through 200 micrometer.

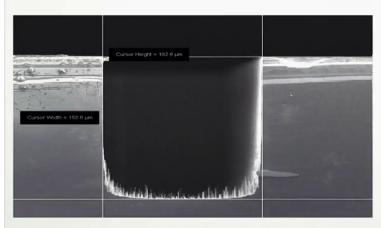

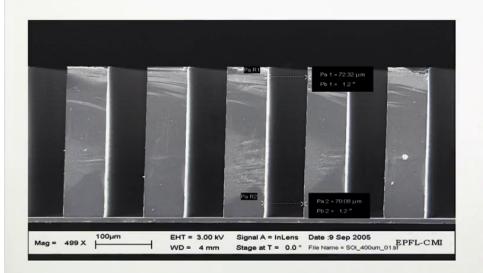

#### **Etching through a SOI wafer by the pulsed process**

- Etch time: 60 min

- Etch depth: 400 μm

- Feature size: 70 μm

- Mask material: SiO<sub>2</sub>

- Si:SiO<sub>2</sub> selectivity is 200:1

- Wafer diameter: 100 mm

- Etch rate: 6.6 μm/min

- Mask undercut: about 2 μm

Micro and Nanofabrication (MEMS)

This picture shows another result of an optimized silicon on insulator wafer etching. The walls are nearly vertical and the etch rate can be very high: more than 6 micrometers per minute, in this case. The etch depth in this case was very high: 400 micrometers.

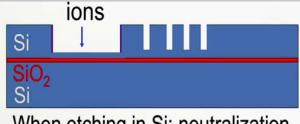

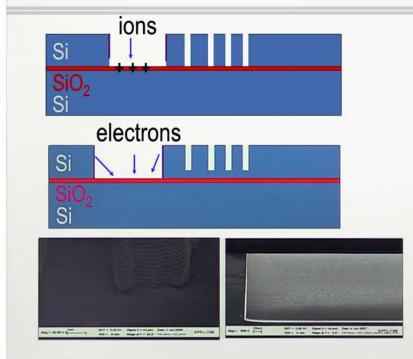

#### Notching effect in the pulsed process

When etching in Si: neutralization of positive charges by the Si

When reaching SiO<sub>2</sub>: charging of oxide and 'footing' or notching effect

#### Continuous RF(13.56 MHz) voltage biasing

Micro and Nanofabrication (MEMS)

However, one can also encounter unexpected results during the etching of an SOI wafer as shown in the pictures on the right. When going lower in the hole structure, one gets increased etching and roughness with even a much bigger hole etched just near the silica layer. This effect is known as the <i>footing</i> or <i>notching</i> effect and can be explained as follows: As long as one etches through the top silicon layer, as shown in this picture, the normal etching and polymerization cycles result in vertical sidewalls. However, when reaching the embedded oxide layer, due to its insulating properties, it can be charged by the ions from the plasma so that further incoming ions get deflected and give enhanced etching in this direction. That is what we have seen here. And you see the same in this picture where the lower part of a narrow, movable beam has been etched away.

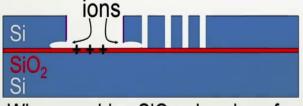

#### Solution to the notching effect: discharging the oxide

- Pulsed process with pulse duration from a few ms to tens ms with an adjustable duty cycle of 10 to 50%

- Ion bombardment is pulsed; in the period without energetic ion bombardment, electrons can discharge the buried SiO<sub>2</sub>

Micro and Nanofabrication (MEMS)

This footing effect can be avoided when one gives sufficient time to the positive ions to be evacuated to the plasma. This is achievable by a pulse process with short pulse duration and reduced duty cycle resulting in a pulsed ion bombardment, and then one waits and there is a compensation of these charges by electrons from the plasma. In this way, structures with vertical sidewalls down to the oxide layer can be obtained as shown here. So this is the lower part of a silicon structure and this is the oxide layer.

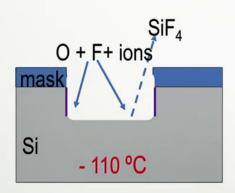

## Deep dry etching of Si: cryogenic process

- SF<sub>6</sub> + O<sub>2</sub> chemistry

- O<sub>2</sub> is the passivation gas

- Etching and passivation are simultaneous

- Substrate temperature: -110 °C

- High etch rate: 1 to 10 µm/min

- Very high selectivity to thermal SiO<sub>2</sub> > 3000

- Very high selectivity to photoresist > 500

- Micro-loading and loading effects are present

- Advantages: free of polymer, no reactor contamination and smooth sidewalls

Micro and Nanofabrication (MEMS)

Another technique for the deep dry etching of silicon is the so-called <i>cryogenic process</i>. The silicon wafer in this case is brought at a temperature of -110° Celsius. And one uses SF6 and oxygen chemistry. SF6 is the etching gas and oxygen is the passivation gas for protecting the sidewalls with oxides. This process does not require a polymerization gas which eventually avoids reactor contamination. High etching rates, up to 10 micrometer per minute, can be obtained. And at this low temperature there is a very high etching selectivity when using silicon dioxide or photoresist as the mask. So these are the selectivities which are indeed very high: 3000 and 500.

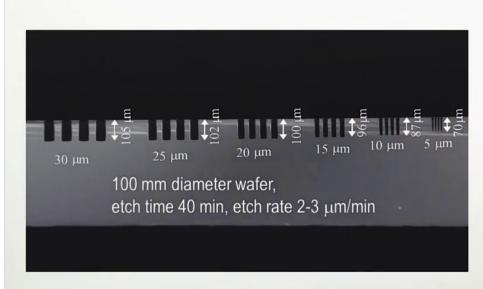

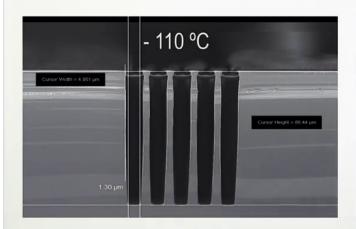

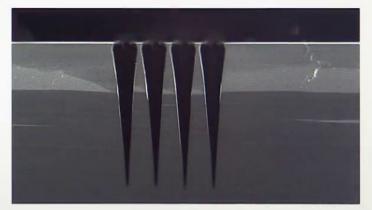

#### Deep dry etching of Si: cryogenic process

Etching shape depends on feature width

Micro and Nanofabrication (MEMS)

These pictures show the etching performance of the cryogenic process. Holes with different diameters are etched and show vertical sidewalls indeed. For a hole with a feature width of 5 micrometers some mask underetching can be observed and there is a reduced etching rate at the bottom of such a narrow hole. The hole with the bigger feature width shows nicely vertical walls on the scale of the microstructure.

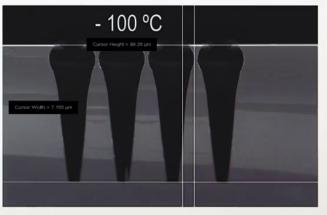

#### Dependence on cryogenic temperature

Etching shape depends on cryo-chuck temperature

Micro and Nanofabrication (MEMS)

The etching profile depends in a sensitive way to the temperature of the substrate which is also the temperature of the chuck on which the substrate is fixed. If one raises the temperature from -110° Celsius, where everything goes pretty well, to -100° Celsius, mask underetching becomes much more important. Clearly the chemical reactions involved in the etching and sidewall protection in this process depend in a very sensitive way on the temperature. And the balance between the two processes is easily disturbed.

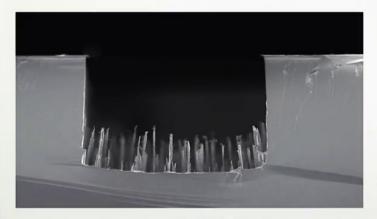

## Dependence on $O_2$ flow rate

# Increase of the O<sub>2</sub> flow rate leads to

grass generation (width 100 µm)

positive shape generation (width 5 µm)

Micro and Nanofabrication (MEMS)

Also, an oxygen flow rate variation can result in less well-defined hole structures. For example, we can see here grass at the bottom of an etched hole because there was too much oxygen supply. If there is too much oxygen, we will have too much passivation and we can also see deviations from verticality when etching through the wafer.

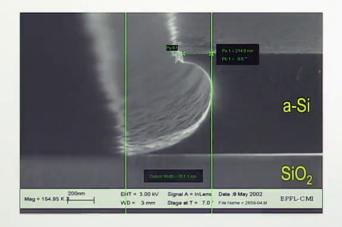

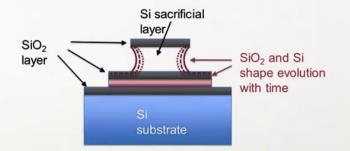

#### **Isotropic dry etching of Si**

#### Use of a SF<sub>6</sub> plasma

Cross-section of an amorphous Si (a-Si) sacrificial layer and SiO<sub>2</sub> layer shape evolution during the release step

Micro and Nanofabrication (MEMS)

While a lot of work has been focused on generating anisotropic silicon microstructures, it is of course also possible to design an isotropic dry etching process for silicon. Here one can use the gas SF6 which has a predominantly chemical action on the silicon. The picture shows the result of such etching, while the diagram here shows the structure, how it was realized. It consists of several silicon dioxide layers and in between two of them is an amorphous silicon layer and it is this amorphous silicon layer that has been isotropically etched, which is shown in this picture here.

#### **Summary**

- Dry etching processes of SiO<sub>2</sub>,Si<sub>3</sub>N<sub>4</sub> and Pyrex glass

- Three processes for anisotropic etching of Si

- Continuous room-temperature

- Pulsed room-temperature

- Cryogenic

- SF<sub>6</sub> process for isotropic etching of Si

Micro and Nanofabrication (MEMS)

This brings us to the end of this short overview of deep dry etching processes that are used in the clean room to etch important microfabrication materials like silicon dioxide, Pyrex glass, silicon nitrite and silicon. For anisotropic silicon etching we have introduced continuous room temperature etching where there is simultaneous polymerization and etching, followed by pulsed room temperature etching, where one alternates the etching and polymerization cycles. And finally, cryogenic etching where oxygen gas passivation replaces the vertical sidewall protection using polymer layers. Also we mentioned the isotropic etching of silicon in a pure chemical etching plasma.